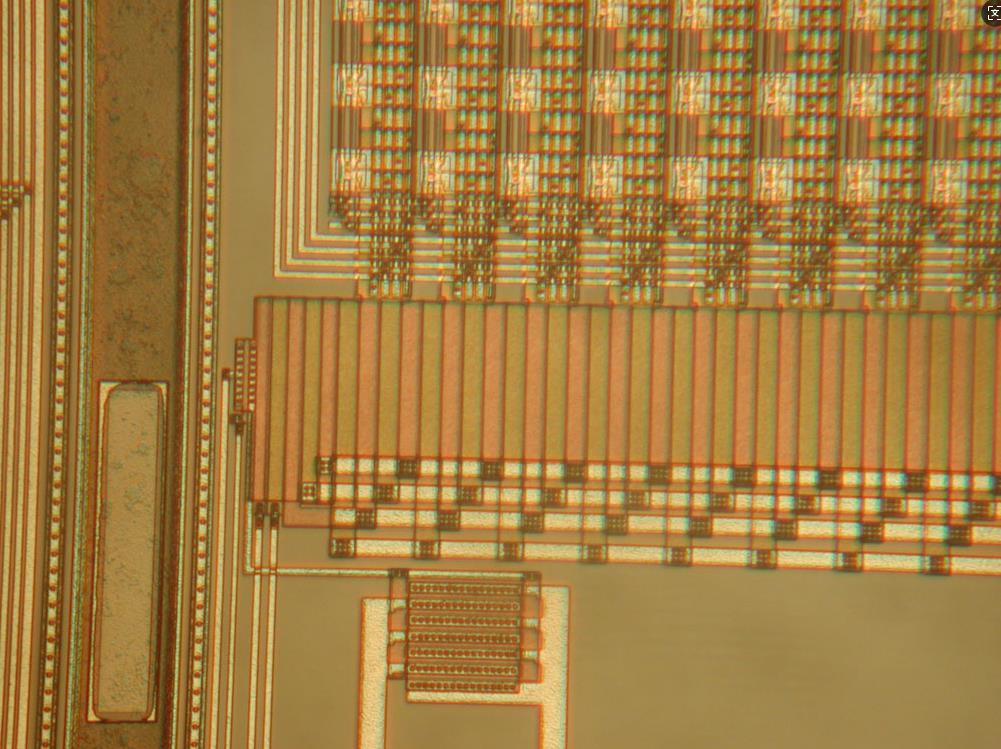

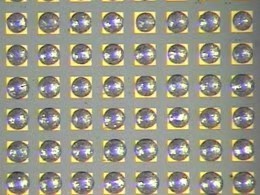

The ASIC-CD chip can be coupled with CZT semiconductor detectors for direct electrical signal readout, or integrated with sodium iodide (NaI) or other scintillator crystal detectors for indirect signal readout via the photoelectric conversion mechanism on the CCD chip.

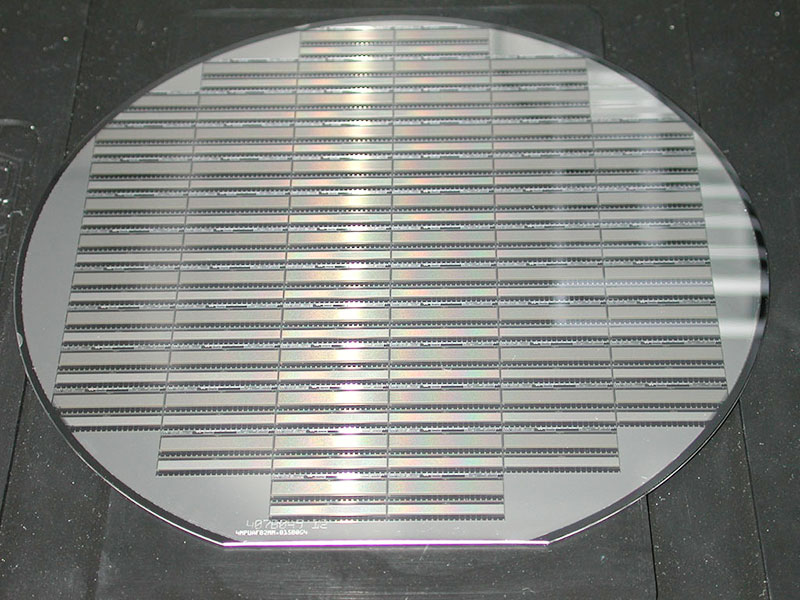

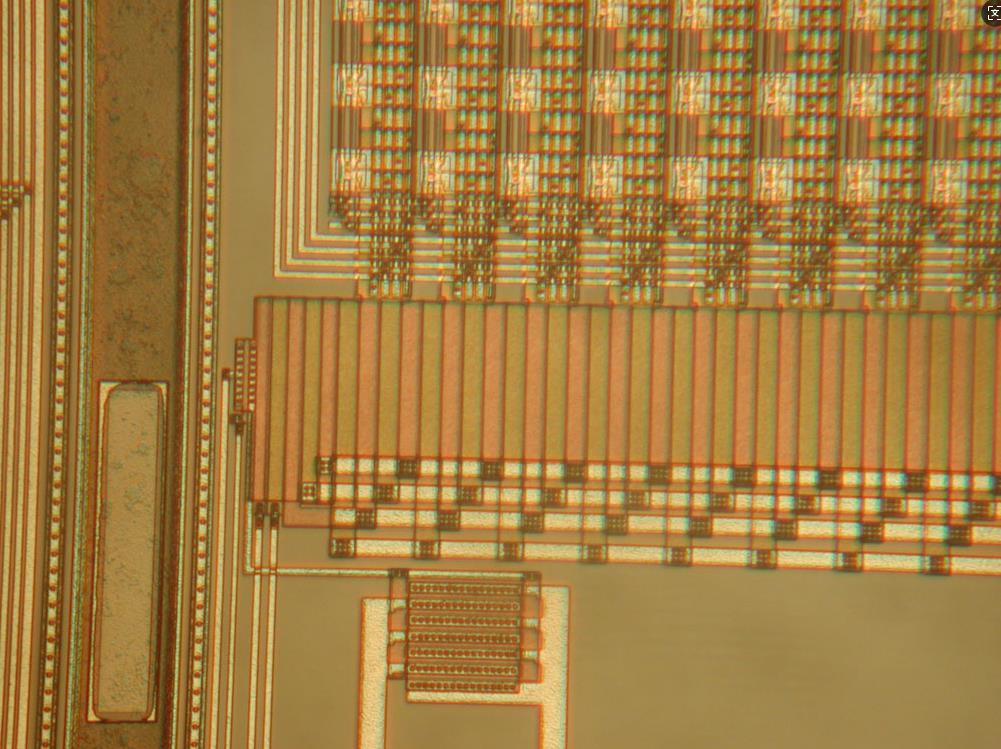

These chips from CRS have a geometric dimension of approximately 20mm (length) × 5mm (width). When multiple chips are cascaded, they form X-ray scanning imaging modules with a scanning length of 400mm or even longer. Their applications span various fields, including industrial flaw detection and medical imaging.